產品列表PRODUCTS LIST

一些 5G 系統的制造商正在轉向更高水平的硬件集成,并在片上系統(SoC)設備中整合射頻轉換器和基帶處理引擎,以解決功耗和電路板空間問題。雖然這種集成有好處,但負責這些系統表征的工程師面臨著訪問數據的新挑戰,因為之前的獨立射頻數據轉換器現在將與 FPGA 和處理器在同一芯片上進行組合。

另一個困擾工程師的因素是 5G 標準本身。作為一種新標準,5G 很可能會向前發展,因此工程師們不僅需要應對如何在集成設備中獲取表征數據的變化,還需要應對參考波形和性能標準可能發生的變化。這給表征過程增加了額外的負擔,它需要足夠的靈活性來應對不斷變化的需求。

為了能夠通過 SoC 進行數據訪問并應對可能不斷變化的標準,理想的表征環境需要靈活的信號生成和分析能力,它不僅能夠生成符合當前 5G 標準的波形,還可以隨著標準的發展生成新的波形。這種信號生成和分析能力還需要能夠從新的 SoC 硬件中提取射頻數據,而不需要射頻工程師成為 SoCs 編程方面的專家。

如果這種信號生成能力與信號捕獲和分析能力包含在相同的桌面環境中,工程師可以執行許多射頻測試和表征任務,而不需要傳統的臺式測試設備。

虛擬測試設備與傳統測試設備

雖然總會有地方放置臺式信號發生器、頻譜分析儀和其他相關傳統測試設備來驗證系統性能,但是這些儀器的成本和物理尺寸使得它們在系統設計的初始表征和“假設”階段不那么受歡迎。允許算法開發人員、射頻工程師和系統設計人員訪問他們的虛擬測試“實驗室”可以加速設計迭代,并幫助更快地獲得佳設計。

硬件和算法的不良選擇可以在設計過程的早期被剔除,而不會占用昂貴的共享資源,如臺式測試設備,更不會占用擁有該設備的相關測試人員。同樣,在進行更廣泛的測試過程之前,可以快速識別出良好的設計理念,并將其發展到更高的程度,大大提高通過認證的可能性,而無需大量的硬件返工,從而節省了開發時間和成本。

這里的目標不是取代桌面測試,而是在過程的早期添加基于軟件的測試,從而降低硬件原型構建成本并提高工程生產率。

但是,這類桌面特征化環境如何與 5G 系統開發的原型硬件一起使用呢?圖 1 顯示了 SoC 設備的軟件表征設置,該 SoC 設備由集成了可編程邏輯和基于 MCU 的處理系統的 8 通道射頻 ADC 和 8 通道射頻 DAC 組成。

圖 1. 連接到基于 PC 的測試環境的 EFSoC 開發工具包

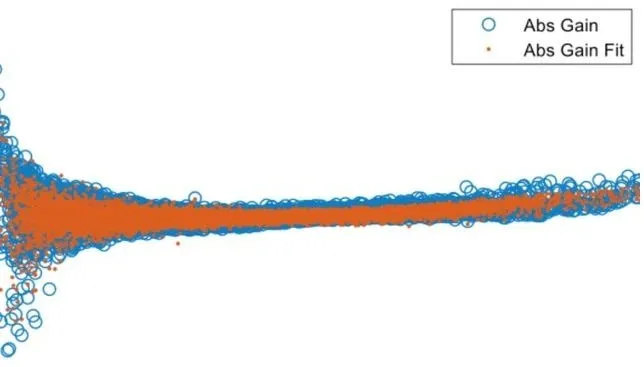

信號將通過 MATLAB 應用程序在 PC 上生成,然后發送到 Zynq UltraScale+ RFSoC 設備,輸出設備的 DAC,通過 ADC 后返回 PC。基于 PC 的應用程序 RFSoC Explorer 將管理數據傳輸、信號生成和各種分析功能,如圖 2 所示。

圖 2. RFSoC 資源管理器表征描述工具的截圖

這種“閉環”測試可減少對外部測試設備的需求,并允許用戶將 RFSoC 上的 ADC 和 DAC 的性能表征到足以對硬件的適用性做出判定的到水平。

這種基于軟件的測試方法使射頻工程師能夠訪問嵌入 SoC 中的數據轉換器,而無需對設備本身進行編程來實現數據訪問,并提供信號生成所需的靈活性,允許用戶在標準發展時根據需要修改波形。

擴展測試方法

雖然基于軟件的測試方法能夠快速做出有關適用性的決定,但也有局限性,主要是硬件和主機之間通信通道的速度和測試軟件本身進行信號分析的速度。如果測試要求更快的信號分析數據速率,則可以使用相同的軟件前端生成信號,將傳統的測試設備連接到 RFSoC 輸出端進行數據分析。這種方法仍然允許波形可編程性,同時緩解了潛在通信瓶頸的影響。

附加測試場景包括使用 RFSoC 設備上的可編程邏輯作為其自身的信號發生器,或在設備中添加邏輯以創建其自身的測試場景,例如對傳入數據設置某些觸發條件,并僅捕獲感興趣的數據以便在 PC 上進一步分析,而不是流式傳輸所有數據。

如有侵權請聯系刪除。